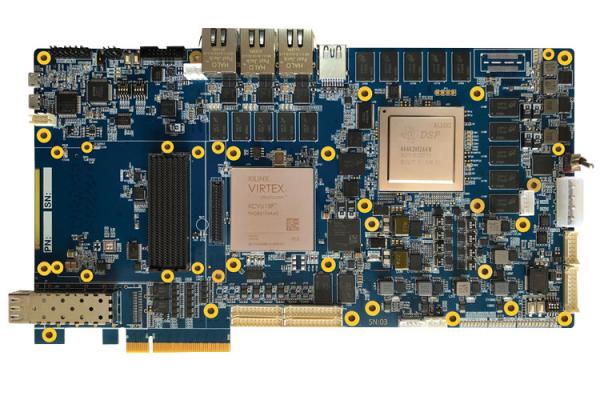

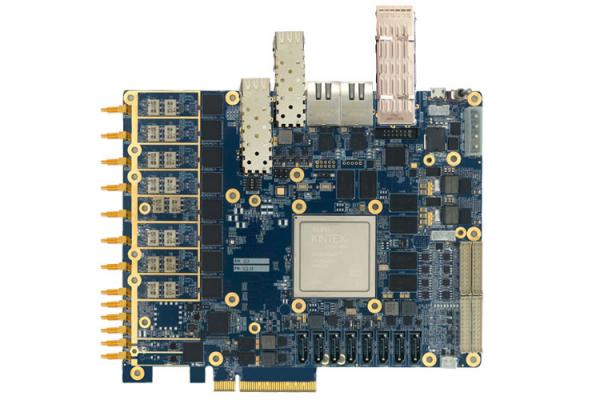

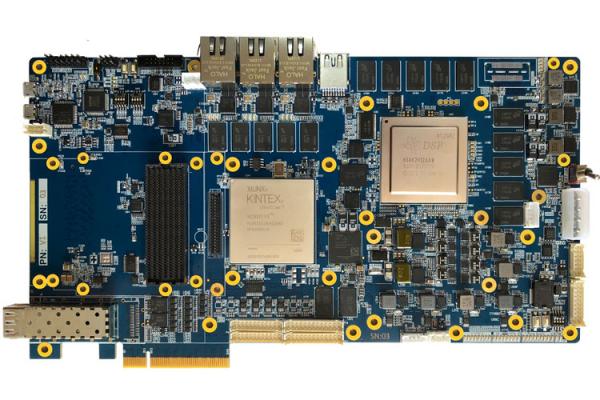

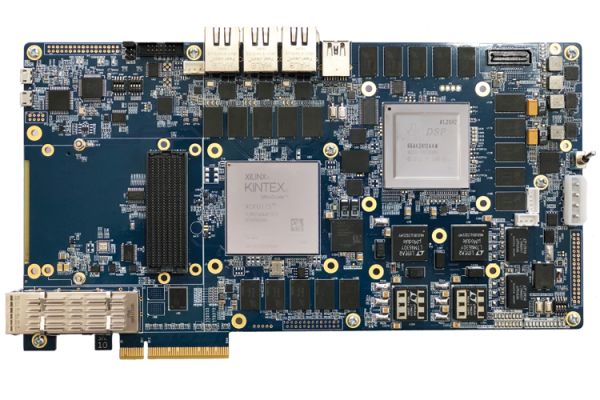

The MYD-C7Z015 development board is a programmable, low-cost and high-performance board designed by MYIR. It integrates Xilinx XC7Z015 (Z-7015) Dual-core ARM Cortex-A9 Processor with Xilinx 7-series FPGA logic from Xilinx Zynq-7000 family, with one PCIe interface and one SFP transceiver module interface on the base board to allow users to expand numerous of high-speed devices. It’s typically applications ranges from Industrial Automation, Test & measurement, Medical Equipment, Aerospace to military and more others.

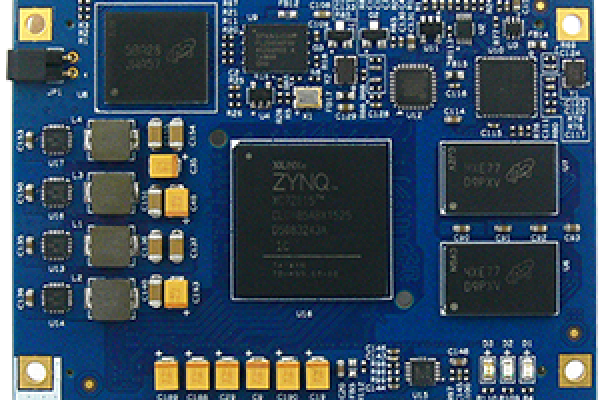

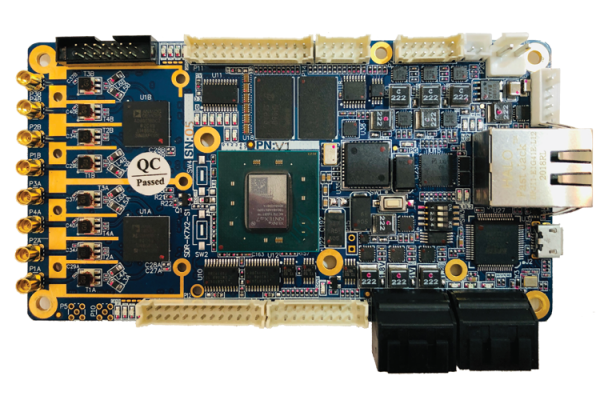

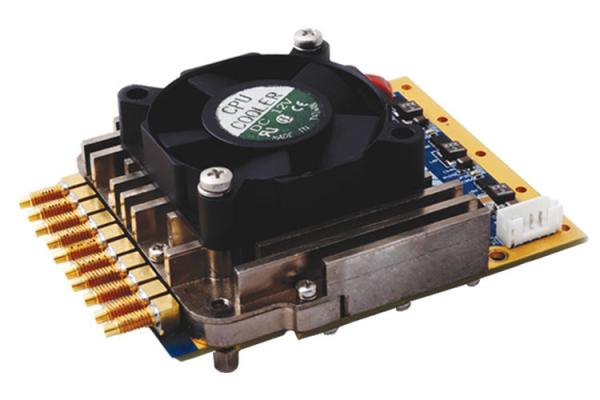

The MYD-C7Z015 development board is using the MYC-C7Z015 CPU Module as the core controller board which integrates the core components including the Zynq-7015 processor, 1GB DDR3 SDRAM, 4GB eMMC, 32MB quad SPI Flash, a Gigabit Ethernet PHY, a USB PHY and external watchdog. The MYC-C7Z015 CPU Module is mounted on to the MYD-C7Z015 base board through two 0.8mm pitch 140-pin Board-to-Board connectors. Compared with the Zynq-7010, the processor Zynq-7015, has more logic cells, Block RAM and DSP slices, which makes the board obtain more powerful programmable function for users.

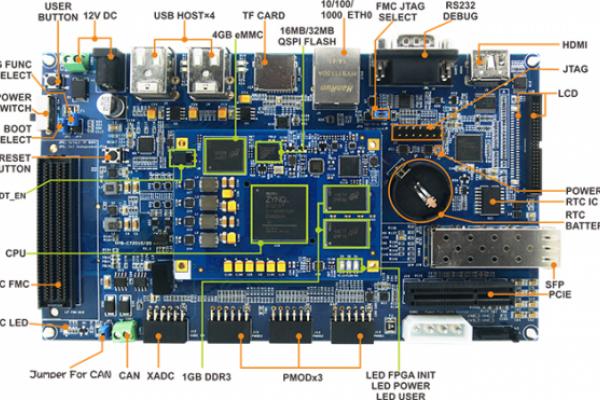

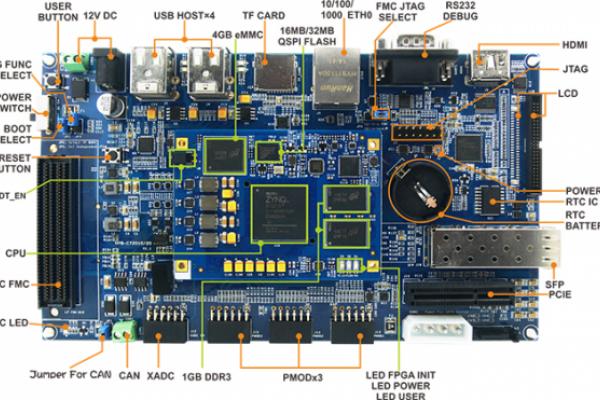

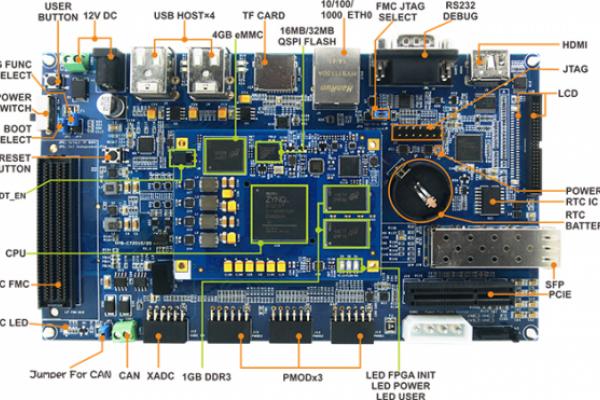

The MYD-C7Z015 development board is using the same base board with MYC-C7Z010/20 Development Board and takes full features of the Zynq-7015 SoC to create a rich set of peripherals to the base board through headers and connectors including one RS232 serial port, four USB Host ports, one Gigabit Ethernet port, CAN, HDMI, LCD/Touch screen, TF card slot, RTC, one XADC header to allow you take advantage of Xilinx XADC, three PMoD headers to meet your I/O needs with PMoDs and one low-pin count FMC connector to allow various FMC cards for custom I/O options. Especially, it has one SFP transceiver moduleto keep higher transmission speed and better stability during your evaluation, as well as one PCIe interface, which contributes the data transmission speed to a high frequency when customers using the board.

The MYD-C7Z015 development board is preloaded with Linux and delivered with necessary cable accessories. It is a high-performance and low-cost development platform for evaluation and prototype based on Xilinx Zynq-7000 All Programmable SoC family.

جهت سفارش محصولات و تسریع در امر سفارشات، مبلغ کالاهای مورد نظر را به یکی از حساب های معرفی شده در لینک زیر واریز نمایید.

جهت سفارش محصولات و تسریع در امر سفارشات، مبلغ کالاهای مورد نظر را به یکی از حساب های معرفی شده در لینک زیر واریز نمایید.